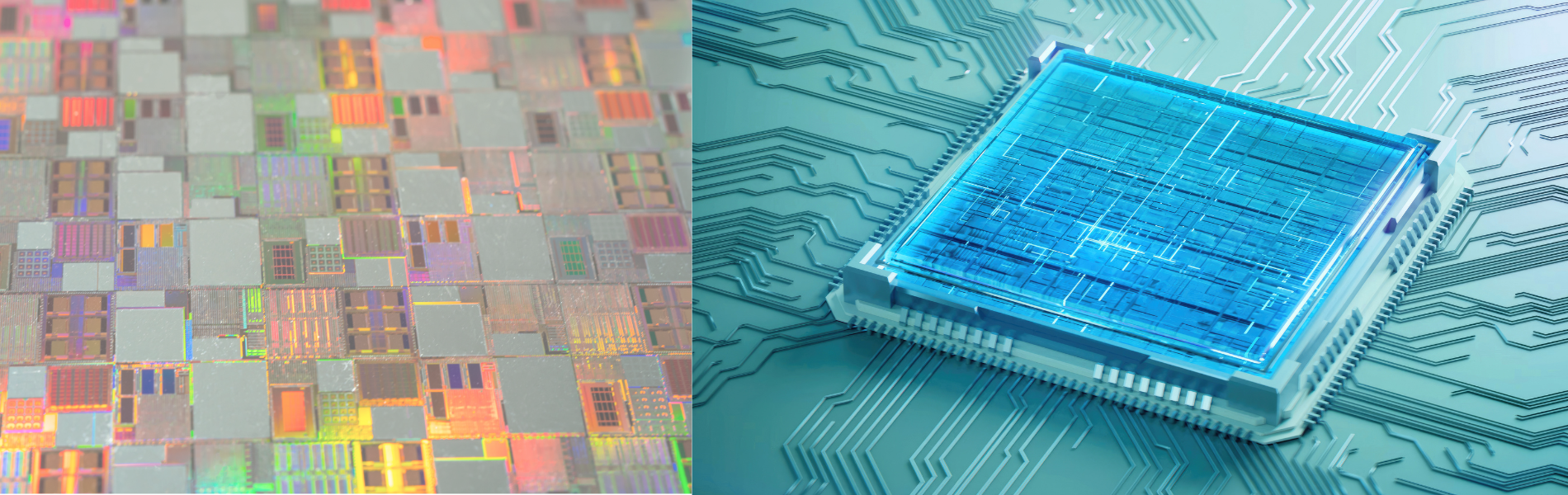

The future of 3D Packaging starts with us

We are a pioneering company seamlessly integrating the heterogeneous integration technologies (CoWoS, EMIB) essential for AI semiconductors with Japan’s semiconductor materials ecosystem, setting new standards for excellence in 3DIC packaging.

A Passion for Pioneering New Technology Concepts from Japan

Our comprehensive range of specialized consulting services meets diverse development needs, from semiconductor equipment and materials to process development.

Research and Study of Advanced Semiconductor Packaging Technologies

Proposing Solutions for Processes, Materials, and Equipment

Promoting Technical Innovation through Customer Collaboration

Monitoring trends, markets, and technical advancements in the latest packaging technologies (e.g., 3DIC). Collaboration with domestic and international research institutes to access cutting-edge technology.

Research and recommendations on optimal process technologies (e.g., CoWoS, EmIB). Evaluating and recommending material selections (e.g., bonding, insulation, thermal management) and supporting new equipment introduction.

Developing solutions for customer-specific technical challenges and creating new packaging concepts. Providing project navigation for product commercialization and optimizing the development process through close communication with customer technical teams.

Collaboration with Japan’s R&D Ecosystem

Technical Consulting on 3DIC Technology

Creation of Technical Content, Education and Training

Strengthening partnerships with domestic materials and equipment manufacturers, universities, and research institutes to accelerate joint research and development projects.

Offering 3DIC-related advice, risk assessments, and recommendations for new technology implementations. Providing seminars, lectures, and training to enhance client knowledge.

Developing technical documents, white papers, and educational electronic content, along with f2f or online trainings and fostering an internal culture of innovation through training programs.

Proven Track Record in Semiconductor Packaging and Collaborative Innovation

Extensive Experience in Advanced Semiconductor Packaging Development

- Engaged in the development of advanced semiconductor packaging technologies at OKI Electric Industry Co., Intel Corporation, Nichia Corporation, and TSMC Japan 3DIC R&D Center.

- Contributed to the establishment of the CoWoS/InFO-oS packaging development line and material development at TSMC’s Tsukuba facility.

- Jointly developed a 16,384-pixel micro-LED integrated into a single ASIC, as part of Nichia’s μPLS headlight project with Infineon, Hella, and Porsche.

- Promoted collaborative development of Intel’s EMIB technology, a key for heterogeneous integration, with partner companies.

- Contributed to the development and mass production of the Flip Chip Ball Grid Array (FCBGA), which became the de facto industry standard as Intel’s mobile Pentium.

- Developed the OKI 400DPI high-density thermal printer head.

- Delivered numerous keynote speeches and published papers at relevant academic conferences.

Technical Expertise

- Semiconductor Package Substrate Technology / Glass Core Substrate Technology

- C4 Flip Chip Assembly Technology

- Cu-Cu / Micro-Bump Interconnect Technology

- Chip on Wafer on Substrate Technology

- Chip on Panel on Substrate Technology

- Embedded Multi-Die Interconnect Bridge Technology

- Underfill / Thermal Interface Material / C4 Solder Technology

- Micro Pixelated Light Source Technology (Micro LED Assembly Technology)

- Member of IEEE Electronics Packaging Society

- Member of The Japan Institute of Electronics Packaging (JIEP)